# Guide to GND Fills and Power Planes

Million 10 60

Designing robust mixed-signal PCBs isn't about one magic trick—it's a system-level approach. Use this guide as your checklist and reference, and you'll avoid common pitfalls that lead to latestage EMC surprises and field failures.

<u>flux.ai</u>

# TABLE OF Contents

| 3 | Why This Guide Exists, What You'll Learn and Ke | y Takeway |

|---|-------------------------------------------------|-----------|

|---|-------------------------------------------------|-----------|

- 5 Ground Fills & Ground-Plane Management

- 8 Stackup Design

- 11 Power-Plane Myths & Best Practices

- 12 "Golden Rules" & Further Resources

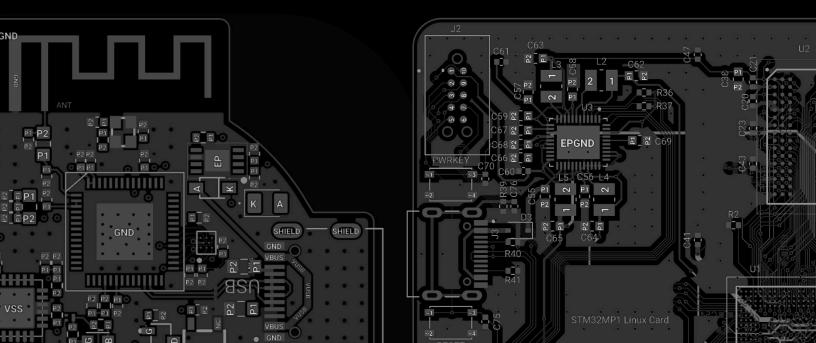

# PCB Stackup & Return-Path Essentials

# Ground Fills, Layers & Planes for Digital & Mixed-Signal Designs

### WHY THIS GUIDE EXISTS

Modern PCBs routinely run signals in the hundreds of megahertz and draw transient currents of several amps in mere nanoseconds. At these speeds, your board's copper geometry becomes part of the circuit: poor return-path planning or an imbalanced layer stack can introduce elusive noise, EMI failures, or even board warpage in manufacturing. This guide—distilled from industry whitepapers, academic research, and decades of hands-on EMI debugging—lays out the principles and "golden rules" you need to design robust mixed-signal boards with confidence.

### WHAT YOU'LL LEARN

| Trace Sizing       | How much current can your narrow copper carry before it overheats?             |

|--------------------|--------------------------------------------------------------------------------|

| Ground Planes      | Why splitting ground is almost always a bad idea—and the rare exceptions?      |

| Stackup Symmetry   | Balancing layer copper to prevent warp and maintain controlled impedance.      |

| Via Stitching      | How and where to place ground-tie vias to crush cavity-mode resonances.        |

| Routing Practices  | Orthogonal vs. broadside coupling—minimizing crosstalk between layers.         |

| Power Distribution | When to use wide traces vs. full power planes and how plane capacitance helps. |

| Cable Shielding    | The physics behind 360° chassis bonds vs. ineffective pigtails.                |

# Fast-Track Cheat Sheet

| PILLAR Trace Capacity | KEY TAKEWAY<br>6 mil & 1 oz Cu $\approx$ 1 A continuous. For 3 A+ use $\geq$ 30–50 mil or<br>heavier copper.                                 |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Single Ground Plane   | Keeps return loops tiny. Splits create detours, high-Q islands, and turn your board into an unintended RF antenna.                           |

| Symmetric Stackup     | Mirror layer order & copper weight around the centerline.<br>Prevents bow/twist and ensures uniform impedance across<br>layers.              |

| Via Stitching         | Place ground vias every $\leq \lambda/10 - \lambda/6$ of your fastest edge-rate wavelength. Ties planes together, killing cavity resonances. |

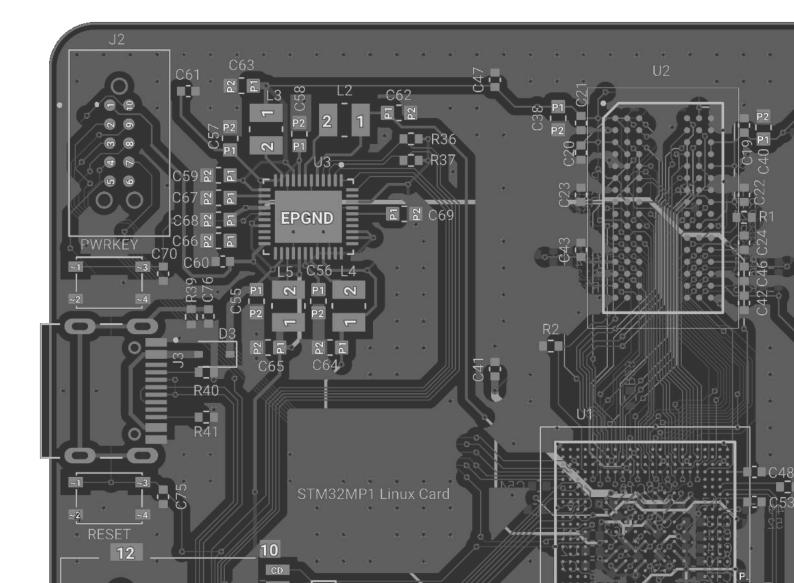

A typical standard 4-layer board

TOP COPPER

MID LAYER 1

MID LAYER 2

BOTTOM COPPER

Learn more at flux.ai

# Ground Fills & Ground-Plane Management

# The Vital Role of Ground Planes

Every high-speed signal completes its electromagnetic loop by sending its return current through the nearest low-impedance path—typically the ground plane immediately adjacent to the trace. When that plane is continuous, the loop area is minimal, inductance is low, and radiated emissions vanish. If the plane is split or interrupted, return current must detour around gaps, **doubling or tripling** the loop area and turning your PCB into an RF radiator.

# Solid vs. Split Ground Planes

| APPROACH                  | BENEFITS                                                                | RISKS & DRAWBACKS                                                 |

|---------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------|

| Single GND Plane          | <ul><li> Lowest loop inductance</li><li> Best EMI suppression</li></ul> | None                                                              |

| TYPICAL USE CASE          |                                                                         |                                                                   |

| One unbroken copper plane |                                                                         |                                                                   |

| tied to 0 V.              |                                                                         |                                                                   |

| APPROACH                  | BENEFITS                                                                | RISKS & DRAWBACKS                                                 |

| Split GND Plane           | Apparent isolation for<br>DC-sensitive analog                           | <ul> <li>Large detour loops increase<br/>ground-bounce</li> </ul> |

| TYPICAL USE CASE          |                                                                         | <ul> <li>Split planes act as dipole</li> </ul>                    |

| Divide ground into analog |                                                                         | antennas at high frequency                                        |

| vs. digital regions.      |                                                                         | <ul> <li>Cavities between islands ca<br/>resonate</li> </ul>      |

|                           |                                                                         |                                                                   |

### In-Depth Explanation:

Splitting ground is often suggested by application notes when designers fear analog and digital blocks won't play nice. In reality, the very act of splitting introduces highfrequency common-mode currents that radiate through the "gap antenna," often **worsening** EMI rather than improving it. Only in extreme cases—where analog offsets are in the microvolt range and physical separation of these blocks is impossible should you consider a split, and even then you must **re-join** the two regions through a single, carefully placed "star" connection (ideally right at the A/D converter).

### When (And How) to Split—Safely

- **1. Absolute Need.** Only if analog nets require sub-10 µV isolation and you cannot layoutpartition your board to keep analog/digital apart.

- **2.** 20·H Separation. Keep analog and digital functional areas at least 20× the dielectric thickness (H) apart to attenuate coupling.

- **3. Single-Point Tie.** Join analog/digital grounds exactly once—use a short trace (or small ferrite-capacitor network) at the conversion boundary.

- **4. Edge-Rate Damping.** Insert a  $1-2 k\Omega$  series resistor on any digital line that must cross the split to slow edges and suppress high-frequency harmonics.

# **Cable Shield Best Practices**

### WHY IT MATTERS

Shielded cables are only effective if the shield forms a true extension of your PCB enclosure. A shield that's grounded by a single solder lug or "pigtail" is high-impedance at RF and lets radiated energy escape—exactly what you're trying to prevent.

| TECHNIQUE<br>360° Chassis Bond | DESCRIPTION<br>Metal-shell connectors (D-<br>subs, shielded RJ45) clamp<br>the cable shield all around to<br>chassis. | PROS & CONS<br>✓ Low inductance, excellent<br>high-frequency shielding                      |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Single-End Pigtail             | One ground wire from shield to PCB ground.                                                                            | X High RF impedance (tens of $Ω$ ), often worse than no shield                              |

| Ferrite/Capacitor<br>Insert    | Ferrite bead or feed-through<br>cap bonds shield at RF while<br>blocking DC.                                          | ✓ Useful for breaking ground<br>loops while preserving RF<br>grounding; moderate added cost |

### Key Insight:

For USB/Ethernet, bond the shield at **both** ends via a low-impedance, 360° connection. If you must break DC continuity, use a feed-through capacitor or ferrite to pass RF to chassis while blocking DC currents.

# Stackup Design

# Why Symmetry Prevents Warpage & Impedance Mismatch

During lamination, copper and FR-4 laminate cure and cool under heat/pressure. **Imbalanced copper** on one side of the board pulls more on that side, causing the board to bow or twist. A **symmetric stackup** (mirrored layer arrangement and total copper weight above/below the midplane) keeps internal stresses in check, yielding mechanically flat boards that also maintain consistent trace-to-plane impedances.

| Stackup Editor |                    | S           | Stackup & Vias Via Hole Configs |             | Stackup Standard 4 Layer - |        |                   |

|----------------|--------------------|-------------|---------------------------------|-------------|----------------------------|--------|-------------------|

|                | Name               | Orientation | Туре                            | Material    | Thickness                  | Weight | Dielectric Consta |

|                | Top Solder Mask    | Тор         | Solder Mask                     | Solder Mask | 0.0254mm                   |        | 4                 |

| 1 🔴            | Top Copper         | Тор         | Signal                          | Copper      | 0.035mm                    |        |                   |

|                | Dielectric 1       | Middle      | Dielectric                      | Prepreg     | 0.1295mm                   |        | 4.3               |

|                | Dielectric 2       | Middle      | Dielectric                      | Prepreg     | 0.1295mm                   |        | 4.3               |

| 2 🥚            | Mid-Layer 1        | Middle      | Signal                          | Copper      | 0.035mm                    |        |                   |

|                | Dielectric 3       | Middle      | Dielectric                      | Core        | 0.7112mm                   |        | 4.8               |

| 3 🔵            | Mid-Layer 2        | Middle      | Signal                          | Copper      | 0.035mm                    |        |                   |

|                | Dielectric 4       | Middle      | Dielectric                      | Prepreg     | 0.1295mm                   |        | 4.3               |

|                | Dielectric 5       | Middle      | Dielectric                      | Prepreg     | 0.1295mm                   |        | 4.3               |

| 4 🥥            | Bottom Copper      | Bottom      | Signal                          | Copper      | 0.035mm                    |        |                   |

| •              | Bottom Solder Mask | Bottom      | Solder Mask                     | Solder Mask | 0.0254mm                   |        | 4                 |

| + LAYER        |                    |             |                                 |             |                            |        |                   |

# **Common Four-Layer Stackups**

| STACK-UP NAME<br>Standard<br>Microstrip | LAYERS (TOP $\rightarrow$ BOTTOM)<br>Signal $\rightarrow$ GND $\rightarrow$ GND $\rightarrow$ Signal | BEST USE CASE<br>General-purpose mixed-signal;<br>both signal layers adjacent to<br>ground planes. |

|-----------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Orthogonal<br>Microstrip                | Signal $\rightarrow$ GND $\rightarrow$ GND $\rightarrow$ Signal                                      | L1→vertical, L4→horizontal<br>routing to eliminate broadside<br>coupling.                          |

| Split-Power<br>Example                  | Signal $\rightarrow$ GND $\rightarrow$ Split PWR $\rightarrow$ Signal                                | Rare; requires thin core & dense stitching to avoid PWR-plane cavities.                            |

### In-Depth Explanation:

A 4-layer board typically uses the two middle layers for power/ground and the outer layers for signals. Mirroring top/bottom makes the board mechanically and electrically balanced. When high-speed or high-power traces must traverse the board, the symmetric build prevents one face from contracting more than the other, which would otherwise warp the board.

# Preventing Broadside Coupling

- Broadside Coupling: Occurs when two traces on adjacent layers run in parallel for a significant length, coupling capacitively and inductively like a parallel-plate structure.

- Orthogonal Routing: By routing L1 traces north–south and L4 traces east–west, any trace crossing is at a single point, slashing coupling by orders of magnitude.

### Quick Tip:

If orthogonal routing isn't possible (e.g. BGA escape lanes), stagger the overlapping length by offsetting the traces horizontally or vertically. Even a small offset dramatically reduces coupling.

# Power-Plane Myths & Best Practices

# When to Use Wide Traces vs. Full Power Planes

| SCENARIO                    | RECOMMENDATION                                                                                     |

|-----------------------------|----------------------------------------------------------------------------------------------------|

| <10 A total, moderate speed | Use wide copper traces ( <i>e.g. 100 mil</i> @ 1 oz for 10 A) + localized decoupling caps.         |

| ≥10 A or GHz-class edges    | Implement a dedicated power plane between ground planes (4-layer or higher) for low PDN impedance. |

# Myth vs. Reality

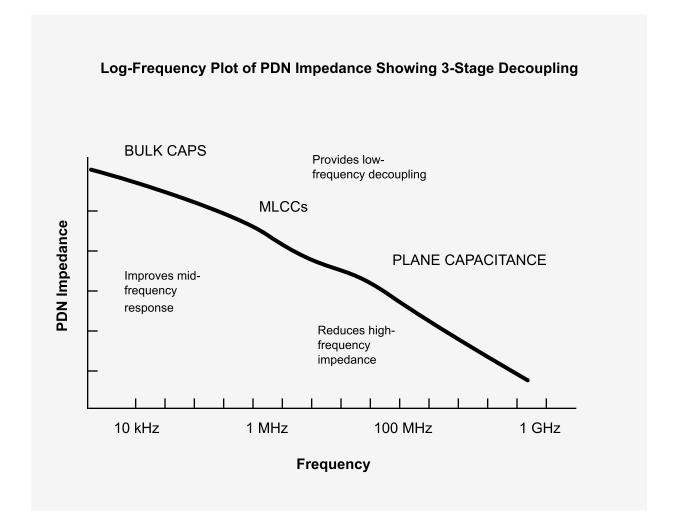

| мүтн<br>Planes embed enough capacitance<br>—skip caps. | REALITY<br>Plane capacitance helps above ~500 MHz, but<br><b>discrete caps</b> are still needed below that to<br>support bulk and mid-frequency decoupling. |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Plane DC voltage must match signal reference.          | AC return paths "see" only impedance. A<br>power plane adjacent to a signal behaves as<br>return via capacitive coupling—DC level is<br>irrelevant.         |

| Ground pours on signal layers suffice.                 | Only a <b>stitch-tied</b> full plane ensures low-<br>impedance return. Unstitched copper islands<br>may resonate and radiate.                               |

# PDN Best Practice Workflow

### 1. Bulk Storage:

Use electrolytic/ceramic bulk capacitors for low-frequency energy buffering.

### 2. Mid-Freq Decoupling:

0.1–1  $\mu$ F MLCCs close to each IC handle switching currents in the 10–100 MHz range.

### 3. High-Freq Shunting:

Plane-to-plane capacitance (and 0.01  $\mu$ F–0.001  $\mu$ F caps) cover 100 MHz–1 GHz noise.

### 4. Plane Stability:

Sandwich power between ground on inner layers with thin core to minimize PDN impedance.

### 5. Stitch Vias:

Tie planes together every  $\leq \lambda/10 - \lambda/6$  to break up cavity modes and lower loop inductance.

# Golden Rules & Further Resources

# Your "5-Step" Golden Rules

### 1. Size Traces Appropriately

- 20 mil for ~3 A; 50-100 mil for ~10 A at 1 oz copper. Always check IPC-2152 charts.

### 2. Never Split Ground Planes

– Unless you have a compelling sub-10  $\mu$ V analog need and no layout alternative. Use a single star-tie if you must.

### 3. Mirror Your Stackup

- Keep copper weight and layer order symmetric to avoid warp and impedance drift.

### 4. Keep Returns Adjacent

Any signal layer must ride alongside a continuous plane. Use orthogonal routing between signal layers for crosstalk control.

### 5. Stitch Everything

– Ground and power planes, copper pours, and critical splits all get vias every  $\leq \lambda/10 - \lambda/6$  at your highest edge frequency.

# Bonus Tips:

- Use PDN simulators (e.g. Cadence Sigrity, Keysight ADS) to identify resonances before you lay out.

- **Build a small test coupon** with ground splits or plane cavities to measure real-world EMI before full production.

- **Probe carefully:** use low-inductance spring-loaded tips and 1 GHz+ scopes when validating return paths.

# **Further Reading**

- TI App Note: "Power Distribution Network Design"

- Analog Devices: "Decoupling Techniques for High-Speed Converters"

- Intel: "High-Speed Board Stackup and PDN Best Practices"

- IPC Standards: IPC-2152 (Trace Currents), IPC-2221 (Generic PCB Design)

- Academic Papers: Search IEEE Xplore for "PCB cavity resonance" and "broadside coupling" for in-depth theory.

- Robert Feranec Youtube's Channel:

"Ground in PCB Layout Separate or Not Separate?"

"Do You Really Need Power Planes? Are You Sure?"

## Author Ryan Fitzgerald

Designing robust mixed-signal PCBs isn't about one magic trick—it's a system-level approach. Use this guide as your checklist and reference, and you'll avoid common pitfalls that lead to late-stage EMC surprises and field failures.